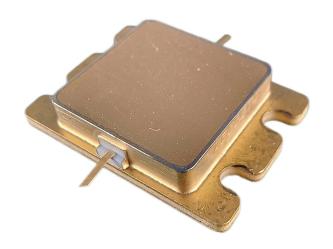

## MCNI2737-P52

## **S-Band Internally Matched Power Transistor**

## **Key Features**

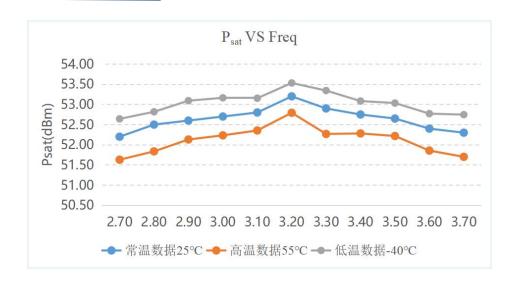

Operating Frequency: 2.70-3.70 GHz

Saturated Output Power (Psat): ≥ 52 dBm

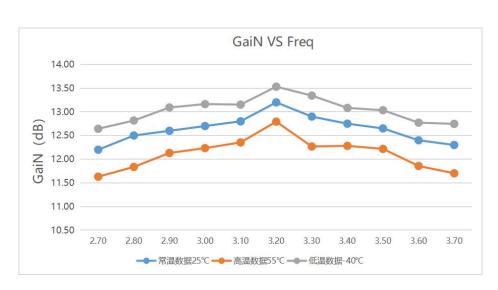

■ Power Gain: ≥12dB

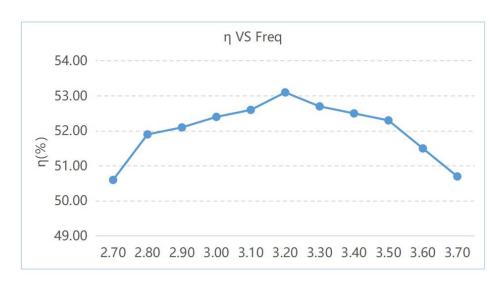

Power-Added Efficiency (η): ≥ 50%Port Matching: Zin/Zout = 50 Ω

#### **Product Description**

The MCNI2737-P52 is a gallium nitride (GaN) internally matched power transistor. Utilizing advanced planar internal matching synthesis technology and mature thin-film hybrid integration processes, it operates in the 2.7–3.7 GHz frequency band. The device delivers high power, exceptional efficiency, and robust environmental adaptability (e.g., temperature stability), making it suitable for diverse RF/microwave systems.

### **Absolute Maximum Ratings (Tc=25°C)**

| Parameter            | Symbol          | Value       | Unit |

|----------------------|-----------------|-------------|------|

| Drain-Source Voltage | V_Ds            | 40          | V    |

| Gate-Source Voltage  | V <sub>GS</sub> | -5          | V    |

| Storage Temperature  | Tstg            | -65 to +150 | °C   |

| Channel Temperature  | Tch             | 150         | °C   |

<sup>\*</sup>operation under these conditions is not recommended

#### **Microwave Electrical Characteristics**

| Parameter              | Symbol           | Test Condition                                                     | Min  | Тур | Max | Unit |

|------------------------|------------------|--------------------------------------------------------------------|------|-----|-----|------|

| Drain Current          | <b>I</b> dsr     |                                                                    | -    | 9.9 | -   | А    |

| Saturated Output Power | P <sub>sat</sub> | VDS:32V Pulse Operation T=1ms,Duty=10% Pin: 49dBm Freq: 2.7~3.7GHZ | 52   | -   | -   | dBm  |

| Power Gain             | Gp               |                                                                    | 12   | -   | -   | dB   |

| Power-Added Efficiency | η                |                                                                    | 50   | -   | -   | %    |

| Gain Flatness          | ΔG               |                                                                    | -0.8 | -   | 0.8 | dB   |

# **S-Band Internally Matched Power Transistor**

# **Typical curves**

# **S-Band Internally Matched Power Transistor**

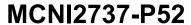

## Recommended application circuit

#### **DUT: Device Under Test**

C1:8pF Rp:51 $\Omega$  C2:1000pF Rg:15 $\Omega$

C3:100uF

# **Electrostatic protection level**

| ESD | Class III | 2000V |

|-----|-----------|-------|

|-----|-----------|-------|

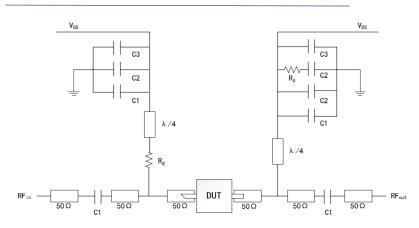

#### **Overall dimensions**

### **Using Notes:**

- During transportation and storage, ensure proper drying.

- During the use and assembly of the chip, take precautions against static electricity. Wear a grounded anti-static wristband.

- When powering on, apply gate voltage first, then apply leakage voltage.